FPGA—Complex Image Processing algorithm acceleration through Field Programmable Gate Array (FPGA)

“An FPGA implementation of Object-based Feature Extraction Image Processing algorithms”

GDA Corp. is undertaking research to identify and document relevant tradeoffs that affect a Field Programmable Gate Array (FPGA) implementation of Object-based Feature Extraction Image Processing (OFEIP) algorithms. While both object-based classification and reconfigurable computing are being actively researched in industry and academia, no significant effort has been undertaken to classify and document the procedure needed to port OFEIP algorithms to a reconfigurable computing environment. We are developing an object-based feature classification system that will be designed so that computationally-intensive image processing kernels can be reused and offloaded to a reconfigurable computing system. By creating an object-based image segmentation and feature extraction framework, much of the “heavy lifting” work will be done up front. Future applications will involve developing spectral/spatial models for the objects to be classified using previously tested and verified components. This is especially important for an FPGA design, since programming is more difficult and time-consuming. Successful project completion will support rapid decision making by providing feature extraction and classification that allows onboard analysis of sensor data in a reconfigurable computing environment.

As a test bed, GDA Corp. is utilizing a previously developed OFEIP algorithm to investigate the tradeoffs that affect an FPGA implementation of such an algorithm. Through a previous NASA contract, GDA has developed a fully-automated, platform-independent, object-based feature extraction cloud and shadow assessment (CASA) algorithm which is an excellent candidate for FPGA acceleration. The CASA software contains a broad and representative set of techniques commonly employed in object-based feature extraction (e.g., image segmentation, shape and pattern recognition, contextual measurements, etc.) and has been designed in a modular fashion, containing a mix of spectral, spatial, and contextual image processing sub-models. Therefore, this OFEIP algorithm makes a good vehicle for evaluating FPGA implementation for these types of algorithms.

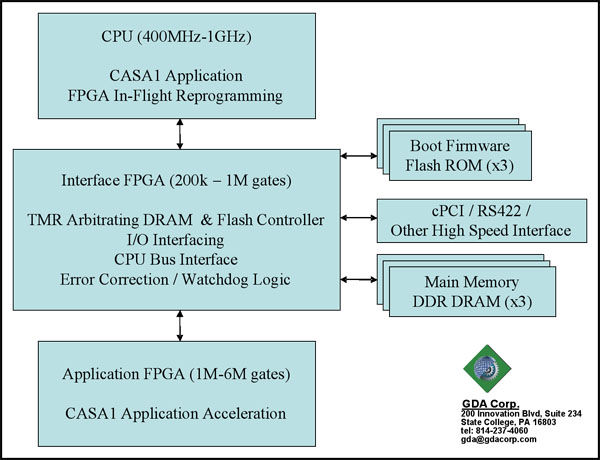

Preliminary CASA Hardware Block Diagram

GDA will classify the individual modules that comprise our test-bed OFEIP algorithm on several scales, including, but not limited to: (i) available parallelism, (ii) ease and effectiveness of porting, (ii) modularization, and (iv) FPGA resource requirements. From this, a representative subset of these modules will be identified and studied in detail by porting to a COTS FPGA development system. This porting will allow GDA to more accurately identify and establish the associated costs and benefits that were initially estimated. Successful completion of this effort will result in the creation of a number of FPGA modules.